This code module provides SPI

- Master support

- Slave support

- Sniffer support

The code module can function as either master or slave, and multiple slave select lines can be implemented as required. Most typical applications are directly supported. SPI sniffer support allows an existing SPI communication setup to be monitored. Speedgoat offers a customisation service to meet any particular requirements you may have.

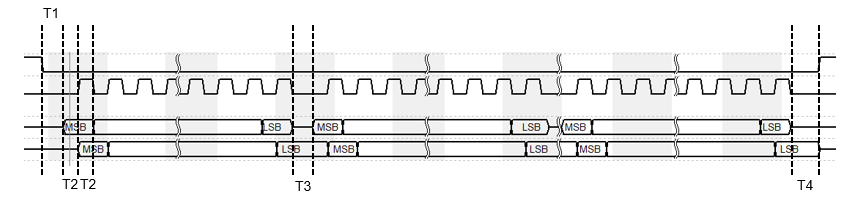

Fig.: An example timing diagram of the signal generated / read by the SPI code module

T 1 = Start delay (master only)

T 2 = Clock divider

T 3 = Inter-word delay (master only)

T 4 = Stop delay (master only)